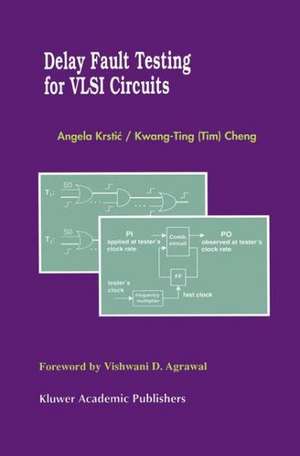

Delay Fault Testing for VLSI Circuits: Frontiers in Electronic Testing, cartea 14

Autor Angela Krstic, Kwang-Ting (Tim) Chengen Limba Engleză Paperback – 12 oct 2012

Din seria Frontiers in Electronic Testing

- 15%

Preț: 614.60 lei

Preț: 614.60 lei - 18%

Preț: 1072.48 lei

Preț: 1072.48 lei - 18%

Preț: 911.64 lei

Preț: 911.64 lei - 18%

Preț: 909.82 lei

Preț: 909.82 lei - 18%

Preț: 915.73 lei

Preț: 915.73 lei - 18%

Preț: 902.39 lei

Preț: 902.39 lei - 18%

Preț: 783.34 lei

Preț: 783.34 lei - 18%

Preț: 909.08 lei

Preț: 909.08 lei - 18%

Preț: 1178.53 lei

Preț: 1178.53 lei - 15%

Preț: 616.36 lei

Preț: 616.36 lei - 15%

Preț: 624.77 lei

Preț: 624.77 lei - 18%

Preț: 906.47 lei

Preț: 906.47 lei - 15%

Preț: 617.72 lei

Preț: 617.72 lei - 18%

Preț: 911.78 lei

Preț: 911.78 lei - 18%

Preț: 918.19 lei

Preț: 918.19 lei - 15%

Preț: 620.23 lei

Preț: 620.23 lei - 15%

Preț: 619.45 lei

Preț: 619.45 lei - 18%

Preț: 914.35 lei

Preț: 914.35 lei - 20%

Preț: 951.83 lei

Preț: 951.83 lei - 18%

Preț: 930.44 lei

Preț: 930.44 lei - 18%

Preț: 910.58 lei

Preț: 910.58 lei - 15%

Preț: 610.96 lei

Preț: 610.96 lei - 15%

Preț: 621.17 lei

Preț: 621.17 lei - 15%

Preț: 614.98 lei

Preț: 614.98 lei - 18%

Preț: 906.03 lei

Preț: 906.03 lei - 18%

Preț: 1172.00 lei

Preț: 1172.00 lei - 15%

Preț: 670.52 lei

Preț: 670.52 lei - 18%

Preț: 921.81 lei

Preț: 921.81 lei - 18%

Preț: 921.04 lei

Preț: 921.04 lei

Preț: 907.57 lei

Preț vechi: 1106.79 lei

-18%

Puncte Express: 1361

Carte tipărită la comandă

Livrare economică 30 mai-13 iunie

Specificații

ISBN-13: 9781461375616

ISBN-10: 1461375614

Pagini: 208

Ilustrații: XII, 191 p.

Dimensiuni: 155 x 235 x 12 mm

Greutate: 0.32 kg

Ediția:Softcover reprint of the original 1st ed. 1998

Editura: Springer

Colecția Frontiers in Electronic Testing

Seria Frontiers in Electronic Testing

Locul publicării:New York, NY, United States

ISBN-10: 1461375614

Pagini: 208

Ilustrații: XII, 191 p.

Dimensiuni: 155 x 235 x 12 mm

Greutate: 0.32 kg

Ediția:Softcover reprint of the original 1st ed. 1998

Editura: Springer

Colecția Frontiers in Electronic Testing

Seria Frontiers in Electronic Testing

Locul publicării:New York, NY, United States

Public țintă

ResearchCuprins

1. Introduction.- 1.1 A Problem of Interest.- 1.2 Overview of the book.- 2. Test Application Schemes for Testing Delay Defects.- 2.1 Combinational Circuits.- 2.2 Sequential Circuits.- 2.3 Testing High Performance Circuits Using Slower Testers.- 2.4 Summary.- 3. Delay Fault Models.- 3.1 Transition Fault Model.- 3.2 Gate Delay Fault Model.- 3.3 Line Delay Fault Model.- 3.4 Path Delay Fault Model.- 3.5 Segment Delay Fault Model.- 3.6 Summary.- 4. Case Studies on Delay Testing.- 4.1 Summary.- 5. Path Delay Fault Classification.- 5.1 Sensitization Criteria.- 5.2 Path Delay Faults that do Not Need Testing.- 5.3 Multiple Path Delay Faults and Primitive Faults.- 5.4 Path Delay Fault Classification for Sequential Circuits.- 5.5 Summary.- 6. Delay Fault Simulation.- 6.1 Transition Fault Simulation.- 6.2 Gate delay fault simulation.- 6.3 Path Delay Fault Simulation.- 6.4 Segment Delay Fault Simulation.- 6.5 Summary.- 7. Test Generation for Path Delay Faults.- 7.1 Robust Tests.- 7.2 High Quality Non-Robust Tests.- 7.3 Validatable Non-Robust Tests.- 7.4 High Quality Functional Sensitizable Tests.- 7.5 Tests for Primitive Faults.- 7.6 Summary.- 8. Design for Delay Fault Testability.- 8.1 Improving The Path Delay Fault Testability by Reducing The Number of Faults.- 8.2 Improving The Path Delay Fault Testability by Increasing Robust Testability of Designs.- 8.3 Improving Path Delay Fault Testability by Increasing Primitive Delay Fault Testability.- 8.4 Summary.- 9. Synthesis for Delay Fault Testability.- 9.1 Synthesis for Robust Delay Fault Testability.- 9.2 Synthesis for Validatable Non-Robust Testable and Delay-Verifiable Circuits.- 9.3 Summary.- 10. Conclusions and Future Work.- References.